Enquanto os modelos de inteligência artificial seguem aumentando de tamanho e complexidade, muitos laboratórios já encaram um limite bem terreno: a energia necessária para treinar essas redes pode tornar a conta de luz inviável.

Um grupo de pesquisadores na China propôs uma rota pouco intuitiva para contornar esse gargalo: recorrer a componentes analógicos naturalmente imperfeitos, permitir pequenas inexatidões nos cálculos e, com isso, reduzir de forma drástica o consumo energético de sistemas de IA pesados - especialmente os baseados em redes neurais profundas.

O problema energético da IA que ninguém consegue ignorar

Treinar modelos grandes de IA, hoje, exige volumes expressivos de eletricidade. Data centers inteiros são dedicados a mover e processar bilhões de parâmetros em supercomputadores com GPUs potentes. A cada iteração de treinamento, a rede neural ajusta pesos - e isso implica novas leituras e, principalmente, novas escritas em memória, operações caras tanto em tempo quanto em energia.

Com a popularização de grandes modelos de linguagem (LLMs) e de geradores de imagem, a curva só acelera. Projeções apontam que, se não houver mudanças na arquitetura (e não apenas “ajustes” de software), o consumo energético da IA pode virar um freio econômico e ambiental, limitando a expansão do setor ou forçando investimentos pesados em infraestrutura elétrica.

A abordagem chinesa descreve redes neurais capazes de aprender gastando até um milhão de vezes menos energia do que sistemas baseados em GPUs.

Esse salto não depende apenas de otimização de código: ele vem de alterar o modo como o cálculo é feito, aproximando o hardware de um comportamento mais “biológico”, no qual processar e lembrar estão intimamente conectados.

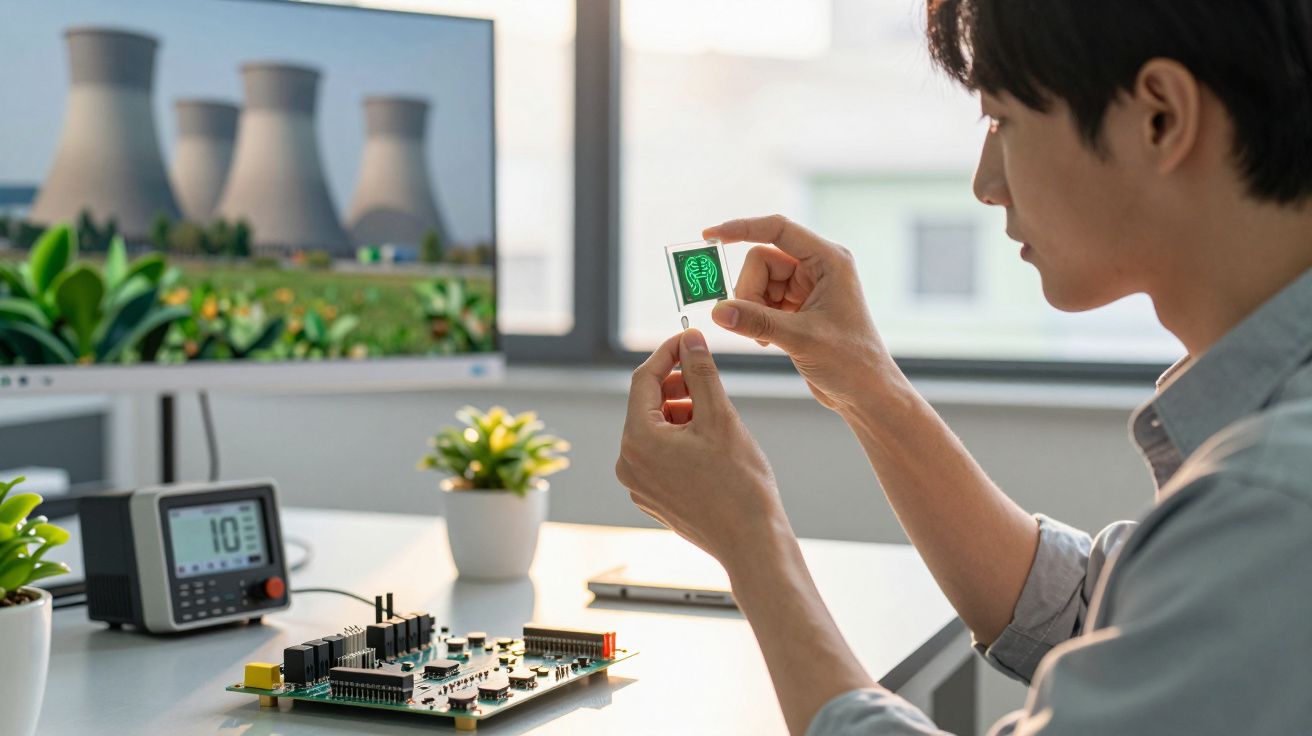

Memristores e computação em memória analógica: os “neurônios” de hardware

O coração da proposta é o memristor, um componente eletrônico ainda restrito, em grande parte, ao meio técnico. Diferentemente de um resistor comum, o memristor tem “memória”: seu estado elétrico reflete o histórico de corrente que passou por ele. Na prática, funciona como uma sinapse artificial que registra o nível de estimulação recebido.

Isso viabiliza a computação em memória analógica, uma ideia poderosa: executar as operações da rede neural no próprio local onde os dados ficam armazenados, evitando o transporte constante de informação entre processador e memória (o famoso “vai e vem” dentro do chip), um dos maiores drenos de energia na IA atual.

- Resistência com memória: o memristor altera seu estado e mantém esse novo valor.

- Cálculos locais: as operações são realizadas onde os dados já residem.

- Menos tráfego interno: menos movimentação de bits significa menos energia consumida.

O obstáculo é que esses dispositivos, na prática, são ruidosos e imprecisos. Variações de fabricação, ruído elétrico e limites físicos do material fazem com que o valor armazenado nunca seja perfeitamente estável. Em arquiteturas convencionais, esse tipo de imperfeição pode reduzir a precisão e até desestabilizar o treinamento.

EaPU e memristores: como a atualização probabilística consciente de erros transforma defeitos em vantagem

Pesquisadores de um laboratório em Zhejiang, na China, decidiram inverter a lógica: em vez de tentar eliminar as falhas dos memristores, por que não assumir essas limitações e incorporá-las ao método de aprendizagem? Dessa ideia nasceu o EaPU, sigla para error-aware probabilistic update - em português, atualização probabilística consciente de erros.

Na prática, o treinamento deixa de tentar atualizar, a cada passo, todos os parâmetros de forma insistente. O sistema passa a aplicar mudanças somente quando elas são realmente relevantes, isto é, quando ultrapassam um limiar de erro considerado tolerável para aquele hardware analógico.

Com o EaPU, menos de 0,1% dos parâmetros são atualizados em cada etapa, derrubando o número de operações de escrita - justamente a parte mais cara em energia.

Essa mudança de estratégia produz três efeitos diretos:

- Menos energia por treinamento: em memristores, escrever costuma custar muito mais do que ler; reduzir escritas muda o jogo.

- Vida útil maior: cada escrita contribui para o desgaste do componente; com menos atualizações, a durabilidade cresce bastante.

- Treinamento mais estável: ao não reagir a microoscilações, o método ajuda a filtrar ruído e a estabilizar a aprendizagem.

Números que chamam atenção

Os resultados publicados na Nature Communications foram comparados com outros esquemas baseados em memristores e indicaram ganhos expressivos:

| Parâmetro avaliado | Antes do EaPU | Com EaPU |

|---|---|---|

| Energia de treinamento | Referência | Até 50 vezes menor |

| Vida útil do dispositivo | Referência | Até 1.000 vezes maior |

| Precisão em relação a outros esquemas com memristor | Base | Cerca de 60% melhor |

| Energia versus sistema com GPU | GPU = 1 | ~ 1.000.000 vezes menos energia |

Segundo os autores, a precisão obtida se aproxima do que se observa em supercomputadores digitais tradicionais - só que com um custo energético incomparavelmente mais baixo.

Testes com imagens sugerem caminho para escalar

Para demonstrar o conceito, os cientistas usaram uma matriz de memristores fabricada em 180 nanômetros - um processo que nem está entre os mais avançados. Com esse hardware, treinaram redes neurais voltadas a duas tarefas:

- Redução de ruído em imagens

- Super-resolução, para aumentar o nível de detalhe em fotos e quadros de vídeo

O desempenho ficou alinhado ao de métodos convencionais, mas com consumo de energia muito menor. Isso chama a atenção para usos em visão computacional no “edge” - como câmeras inteligentes e sensores - onde eficiência e compacidade são determinantes.

Redes neurais em memristores podem aproximar a IA avançada da fonte de dados, reduzindo a dependência contínua da nuvem.

Um efeito colateral relevante é a diminuição de latência: ao processar localmente, reduz-se o tempo de resposta e também o tráfego de dados, o que pode ser decisivo em aplicações industriais e de segurança.

A técnica pode chegar aos grandes modelos de linguagem (LLMs)?

A pergunta mais óbvia é se o EaPU conseguiria escalar para os LLMs, usados em chatbots e assistentes virtuais. Os pesquisadores afirmam que a resposta tende a ser positiva, e que a limitação, por enquanto, está mais no hardware disponível no laboratório do que na lógica do método - ainda não havia capacidade física para acomodar redes gigantes.

Como o EaPU não é “amarrado” a uma única tarefa, a expectativa é que qualquer rede neural profunda com muitos parâmetros possa se beneficiar de atualizações probabilísticas e de uma tolerância controlada a pequenos erros. Se isso se confirmar em modelos de linguagem, o impacto no custo de treinamento da IA generativa pode ser enorme.

Além de memristores: outras memórias não convencionais no radar

Outro ponto promissor é que a ideia não parece exclusiva de memristores. O grupo sugere que a mesma filosofia pode ser aplicada a outras tecnologias emergentes de memória e computação em memória, como:

- Transistores ferroelétricos, que aproximam armazenamento e lógica;

- Memória magnética de acesso aleatório (MRAM), já explorada por grandes fabricantes de chips;

- Outros dispositivos analógicos emergentes voltados a computação em memória.

Essa diversidade pode ser crucial para a indústria, porque aumenta as chances de encontrar uma rota de produção em escala que seja estável, economicamente viável e compatível com cadeias de fabricação existentes.

Riscos, desafios e o que ainda precisa ser provado

Apesar dos números impressionarem, ainda existem barreiras até essa abordagem aparecer em data centers comerciais. Produzir memristores em grande escala com comportamento consistente continua sendo difícil; variações entre lotes podem exigir calibração cuidadosa, o que afeta custo, rendimento e confiabilidade.

Também há uma questão de flexibilidade. CPUs e GPUs digitais são generalistas: o mesmo hardware serve para treinar, fazer inferência e executar outras cargas (de simulações a renderização). Já arquiteturas de computação em memória analógica tendem a ser mais especializadas, otimizadas para certos tipos de rede e operações. Isso implica novas ferramentas, novos fluxos de desenvolvimento e, possivelmente, uma reeducação prática para parte da comunidade de engenharia de IA.

Além disso, surgem preocupações de engenharia e qualidade: como garantir repetibilidade quando o sistema depende de componentes analógicos sujeitos a temperatura, envelhecimento e ruído? E como criar rotinas de teste e validação que “conversem” com essa variabilidade física?

Por que aceitar erros pode reduzir tanto o gasto de energia

O ponto conceitual central é que redes neurais, por natureza, não precisam de exatidão matemática perfeita em cada operação. Elas aprendem por aproximação, ajustando parâmetros para reduzir erros ao longo de muitos exemplos.

Nesse cenário, discrepâncias pequenas introduzidas pelo hardware analógico não necessariamente derrubam o desempenho - desde que permaneçam dentro de limites razoáveis. O EaPU tenta justamente encontrar esse equilíbrio: tolerar uma parcela de erro e, ao mesmo tempo, fazer atualizações seletivas para manter o aprendizado eficaz.

Em outras palavras, é uma troca direta entre precisão absoluta e custo energético: aceitar um pouco de ruído para tornar o treino e a operação muito mais baratos. Em contextos onde cada watt conta - de grandes fazendas de servidores a dispositivos alimentados por bateria - essa barganha faz sentido.

Possíveis cenários práticos e efeitos em cadeia

Se arquiteturas desse tipo amadurecerem, alguns desdobramentos ficam mais plausíveis:

- Data centers de IA com consumo muito menor, reduzindo despesas e pressão sobre a infraestrutura elétrica.

- Modelos generativos treinados e atualizados com mais frequência, já que o custo energético deixa de ser tão proibitivo.

- Dispositivos de borda (celulares, roteadores, sensores industriais) rodando IA avançada localmente, com menos dependência de nuvem.

Para o Brasil, essa linha também conversa com desafios práticos: o crescimento de data centers e cargas de IA pressiona planejamento energético e refrigeração, e soluções mais eficientes podem reduzir custos operacionais e facilitar a expansão com menor impacto ambiental. Ao mesmo tempo, para setores como agronegócio e indústria, levar inferência (e eventualmente parte do treinamento) para o edge pode diminuir conectividade necessária e aumentar resiliência em áreas com rede limitada.

Em paralelo, aparecem novas perguntas: como auditar decisões em sistemas analógicos ruidosos? Como estabelecer padrões para reprodutibilidade quando o hardware varia com o tempo? Esses temas ainda pedem pesquisa, métricas e normalização técnica.

Ainda assim, a direção geral é clara: aproximar hardware e aprendizagem - com componentes que calculam e “lembram” ao mesmo tempo - pode enfraquecer a ligação atual entre IA de ponta e consumo energético explosivo.

Comentários

Ainda não há comentários. Seja o primeiro!

Deixar um comentário